主题:3nm准官宣了:即将发表的论文 -- 陈王奋起

2024年3月26日(具体日期待确定),来自中国西湖大学的学者在2024 年SPIE 高级光刻+图案化会议中宣读了一篇论文,标题为:"Mandrel/spacer engineering based patterning and metallization incorporating metal layer division and rigorously self-aligned vias & cuts (SAVC)” 中文是:“基于芯轴/间隔物工程的图案化和金属化结合金属层分割和严格自对准通孔和切割(SAVC)”

在论文记录的是基于一项华为专利,WIPO 专利申请号CN2022/097621,采用两种硬掩模替代通常EUV光刻时的一种硬掩模,实现了相当于常规工艺6倍的分辨率。论文全文会刊登在5 月份出版的 SPIE Proc(国际光学工程学会出版的会议论文集)上。

作者Chen Yijian在自己的Lindedin上更是豪情万丈地写道:我们是否需要高数值孔径 EUV 扫描仪来缩小至 1.4nm逻辑节点(假设最小金属间距约为 12 纳米)?也许193i DUV光刻仍然可以让我们接近这样的金属目标。如何?请查看我们在 2024 年 SPIE 先进光刻 + 图案化会议上的论文(12958-1:纳米图案化会议的先进蚀刻技术和工艺集成)。这是西湖大学将人类工程师的智慧延伸到极致的不懈努力。

我查阅了CN2022/097621的专利文档,其中提到该发明旨在提供一种改进的金属集成解决方案,其可用于制造集成器件的工艺流程中。目标是为各种金属间距提供解决方案,例如,为 21 nm 以下的金属间距提供解决方案。另一个目标是解决 EPE 裕度低于 5 nm 的情况。

半导体行业通常用金属间距的一半作为最小分辨率,上述技术完全可以做到等效3nm。按照Chen Yijian的乐观看法,这项技术的上限是1.4nm,而且不需要EUV,仅仅DUV就可以了。

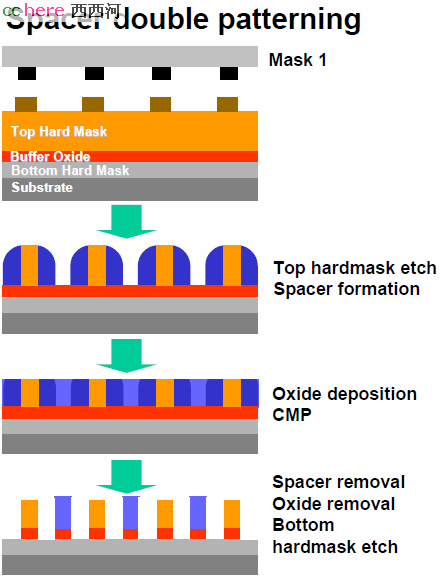

近期彭博社还在为华为鼓吹另一项技术,自对准四图案的技术。所谓自对准,就是用一个图案的两个侧壁来作为阻挡光线层,从而实现了分辨率加倍,误差却不增加的技术,下图是自对准双图形的示意图。大家可以大略了解这个技术:

这项发明专利申请CN117751427A在2024年3月22日公开,申请日是2021年9月1日。和其他自对准四重曝光技术不一样地方在于:相邻的金属线制作在同一光掩模上,则不能使其彼此非常接近,但如果它们制作在两个不同的光掩模上,则可以使其彼此非常接近。这样,在自对准四重图形化技术中进行多次光刻,将相邻的金属线分布在不同的光掩模上,从而达到之前预期达到的效果,并且高密度改进了电路图案设计。

一般认为,配合相位掩膜,计算光学补偿等技术,上述4自对准四图形技术可以达到目前3nm的分辨率。

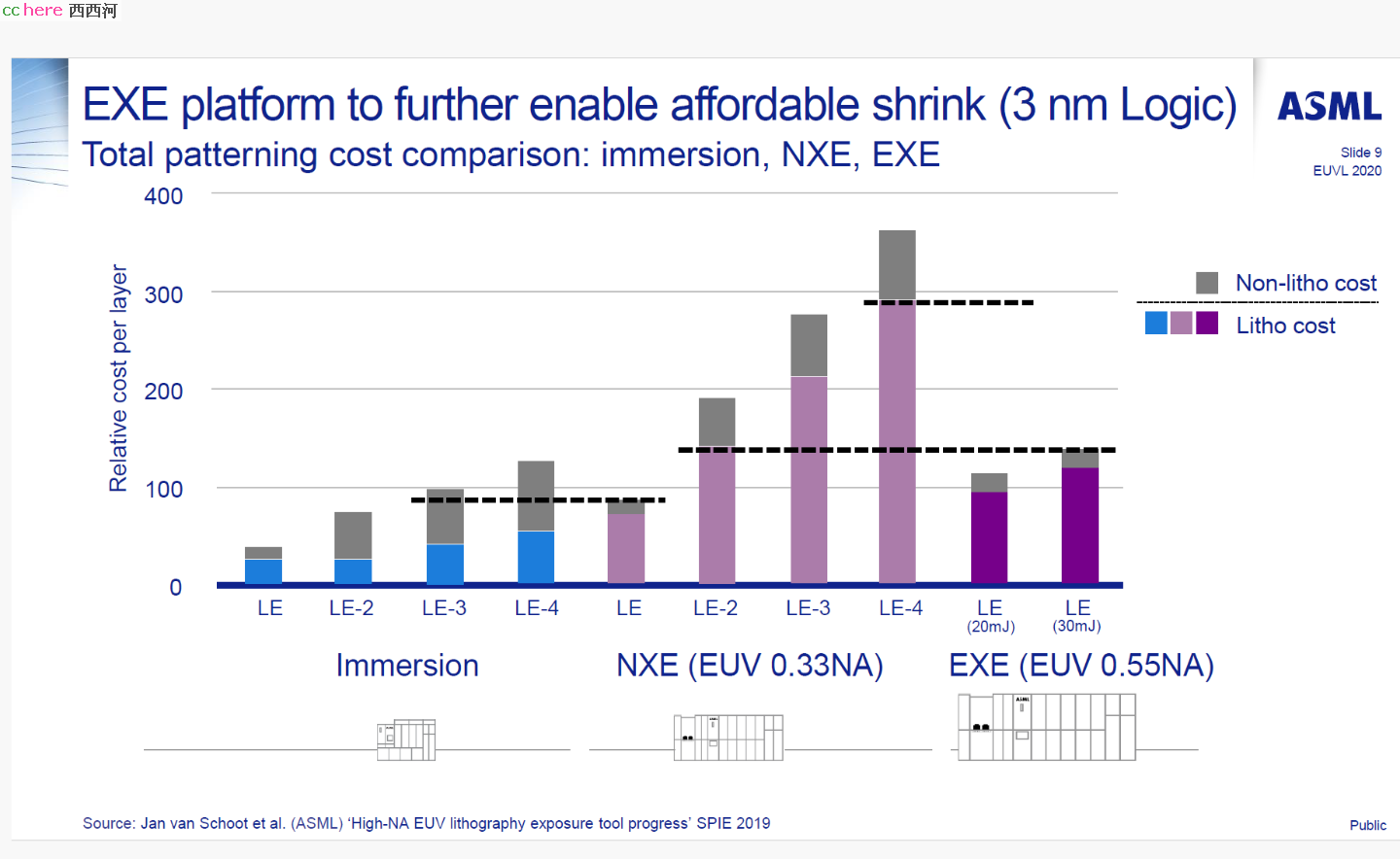

至于成本,可以参考ASML的一个浸入式DUV和EUV光刻的对比,见下图:

在5nm水平,我估计DUV的光刻成本比EUV还低,而且光刻速度更快,产能更高。

至于良率,当初台积电发表7nm的时候是50%不到,一年后75%,最终大概90%。在最新的华为芯片麒麟9000s的设计中,不同区域的密度明显不同,上下相差40%,说明华为掌握了在一个芯片上弹性工艺的设计,EDA也完全可以支持。这样在不需要高超制程的地方,完全可以降低密度,在需要高速的地方,可以提高速度,形成局部3nm,部分地方7-10nm,整体5nm的布局,同时满足速度、成本和功耗的平衡。有这样的技术,我相信华为最终的良品率一定在75%以上。

回头看,华为的实力真是恐怖。2021年,就是3年前华为已经具备了相当的技术实力,引而不发,埋头苦干。中国有华为,幸甚!很多事情,历史上出现一次,是正剧,第二次,就是喜剧了。有这样的技术,小院高墙最终会变成闭关锁国的笑话。

非常感激陈王兄做芯片前沿技术的解读、分析和分享,善莫大焉!

学到了很多,请多多分享!

latch 和SRAM的密度本来就是不一样,所以一个die上面会有不同密度的存在。哪怕是SRAM,也是有不同的密度的。这些不能说明在同一个die上面使用弹性制程的。

本帖一共被 1 帖 引用 (帖内工具实现)

Advanced Etch Technology and Process Integration for Nanopatterning XIII

大家可以看看这个链接里的会议论文摘要。那么多工作,每一个都声称自己巨大进步。但是这种科研人员在某个节点的新思路,和最后落地做到3nm,距离很大。当然真实的做成也是一步步积累来的,每一步很重要,应该庆贺。但也不必过度解读。不要说这么低级别的会议,就是发了nature(工科发nature说比理科难度高两个数量级也不算夸张),十多年不能落地的科研进展也多了去了。

不认识台上发言的人是谁

上面看着挺提气

看着看着就有了一种感觉——

ppt一翻页,赫然出现“夫妻关系”

文科生对这些高科技不太理解,

是不是就像中美对狙击枪的努力:

美国用了____年时间把狙击枪精度提高了____厘米

中国用了____年时间把狙击枪的杀伤范围提高了____米。

你提高你狙击枪的杀伤精度,我提高我狙击榴的杀伤范围。

到芯片这里是不是有这个异曲同工啊?

你的技术路径,实现可行性,成本因素,最终性能,良品率,行业人士马上就能根据这几条估算出工业化落地的可能。

像华为这种,几年前布局国内发明专利,PCT专利,又在国际大会上宣读论文的,几乎肯定是已经做成了,作为一种宣示给合作伙伴或者上下游,其他人才会打起精神,积极合作。

看不懂,计算机白学了。

😭😭

为啥说多次曝光反而比EUV一把过快啊?

3nm后面2nm,1nm,在后面是不是要0.1nm了?普通人也能看出来不对劲了。

将来把几nm换成多少晶体密度也就是mtr比较合适。

bridge , cut没法做,实际只做划线的话有很多低成本的方式

自对准图案化,做1-3层金属层良率并不高,

成本倒是可以跟euv有的拼, 而且tsmc 450w euv上来后速度未必有优势

技术确实可以进步, 像去年做n3b,成本和良率都很难接受,也就是苹果能扛。

但是今年n3e上了以后,就好不少,高通,苹果,amd, intel都准备用

耶奶则准备拖到P70发布后再来

看不清脸,从ppt大字只有口号,没有证据上看,大概率是骗子。稍微有点品的,不管真假起码有几个数据图列在上面。

顺风局,vv不削没法玩了