主题:【原创】在 Multi-die IC Packing 技术面世之前 -- 四月一日

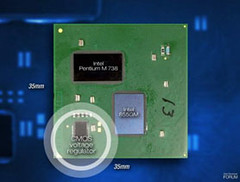

在 Highway 所谈到今年 IDF 的帖中, 提到集成 Intel Pentium M 738 (也就是 LV Pentium M 1.4 GHz CPU) 以及 855GM (这部份有点诡异, 855GM 应该已经被 855GME 完全取代了) 芯片的新产品. 在这个产品中, 除了 Intel 将 CMOS Voltage Regulator 放进芯片中之外, 最引人注意的应该就是在同一个芯片上封入两个 die (P-M 738 CPU 与 855 chipset) 的部份了. 趁着兴头, 就来侃侃这个 multi-die on a chip 的技术吧.

Multi-die on a Single Package

如果这事不是 Intel 干的, 八成会引起不小的猜疑甚至嘲笑, 如 VIA (威盛) 于今年稍早发表的 Luke 便是如此. 左看右看, 这 VIA Luke 整个一个过渡型产品的样子. (由于 VIA 继承所购并的 Cyrix 的 Intel 技术授权的时间所剩不多, 而 Intel 一点也不想给 VIA 这个 competitor 继续授权.) 没想到这边还没笑完, 那边 Intel 在 IDF 大摇大摆产示的新产品也是相同的概念. 天啊, 这 Intel 还真是不争气, 跟在 AMD dual core 的屁股后面也就罢了, 这回竟然连 VIA 的东西也拿来抄!?

VIA Luke 是包了 VIA Eden-N 1.0 GHz CPU core 和 CN333/400 chipset. 使用 EBGA 的封装方式, 成品的 chip 呈长方形. (一般是正方形.)

Intel P-M 738 加 855 chipset 的图片如 Highway 贴过的. 使用的仍然是 Intel 引以为傲的 Micro-FCBGA 的封装方式. 这个集成式 IC 的大小与单一的 Intel 855GM/GME 的大小一样.

当然, Intel 和 VIA 两家的方式仍会有所差异, 产品的级别也不相同. VIA Eden 只相当于 Intel Socket 370 时代的 Mobile Pentium-III Celeron 左右, IS 方面只有 MMX 和 3DNow!, L2 Cache 也不大. Intel 使用的是前一代 (现在仍是主流) 的 Centrino Pentium M CPU 的低功耗 LV 版本, 效能上与一般的 P-M CPU 相当. 不过由于 VIA Eden CPU 和过去 Intel mobile P-III Celeron 相比在制程工艺上先进些 (因为是后来才做的产品, 可以应用较先进的制程技术), 所以在耗能方面的表现是比 Intel Mobile Pentium-III Celeron 好些的, 适合非主流 PC 的嵌入式 x86 计算器平台.

Intel 是抄 VIA 的创意吗? 先看看 multi-die on single chip 的技术演进, 以及在这之前 Intel 做了哪些事.

封装技术与集成技术

要评论这种 Multi-die on single package 的封装方式, 必须由 IC 封装技术的演进谈起. 首先大略介绍一下 IC 的基本组成.

一个芯片的产生, 是先用 mask 在一片 wafer 上刻电路, 然后将 wafer 切割成独立的 die. 这个 wafer 就是俗称的六吋, 八吋, 十二吋的晶圆, 而 die size 就看所要做的 IC 所包含的 gatecount 与所使用的制程工艺技术, 比如 0.18um, 0.13um, 90nm 或 65nm. 在相同 yield rate 的假设下, 如果 wafer 的尺寸愈大而 die size 愈小, 愈能在一片 wafer 上做出更多的 die 出来, 这也表示了成本的降低. 对于像 CPU 这类高 gatecount 高热量的 IC 来说, 愈小的工艺表示能做出愈小的 die 并使用愈低的工作电压, 让 CPU 的成本与耗能愈低. 哦, 跑题了, 回来. ![]()

在把 die 从 wafer 上切割下来之后, 还必须经过封装 (packing) 的工序, 才会成为大家所知道的 IC, 除了 COB 的 IC 之外. (COB 是将 die 直接用 SMT 打在 PCB 上的技术, 一般用在简单且成本十分敏感的小型控制器上.) 一般从 die 到 IC 的工序为:

Die mounting (上芯片) --> wire bonding (打线) --> molding (上胶) --> marking (文字面印刷)

经过上面的工序后, 就进入封装后测试, 然后包装出货. 其中 marking 的工序不一定会做, 因为有些 IC 是以 no-brand 的方式甚至是 wafer 的方式卖的, 如 DRAM 就常以这个方式出货, 将产品以 none-marking 的方式出货给下游的内存条制造商, 让他们自行印上自己的品牌. 这种出货方式相当于下游内存条厂商向上游 DRAM 厂商以合同方式购买 IC, 而 DRAM 厂商会因为内存条市场的竞争特性而让内存条厂商拥有自己品牌的颗粒, 相当于 OEM 的合作模式, 如 kindston 的内存条. 不过由于 marking 的成本与批量要求 (MOQ) 并不是很高, 所以市面上还是会出现一堆打上各家品牌的内存条, 当然还有一些是 remark 的混在其中. 哦哦, 又跑题了, 回来回来. ![]()

![]()

由于市场对于 PC 计算能力的追逐, 让 CPU 与其所搭配的 chipset (自 586 起一般分为 Northbridge 与 sourthbridge) 以及同样强调效能的 GPU 等 IC 面临必须不断革新的需求, 而这也推动了 IC 技术的持续进步. 在 "传统" 的 IC 工艺与封装技术的搭配下, 过去常会因为当时现有的芯片封装技术达不到要求, 而有 "出轨" 的演出. 在最新的 IC 工艺能达到市场需求之前, Intel 利用当时能及的技术, 比较著名的就属 MMC 与 SECC 了.

Intel SECC : CPU and Cache RAM on Single Module

Intel SECC (Single Edge Contact Cartridge) 是将 CPU 与 Cache 放在同一个 CPU module 上, 代表作是 Intel Slot-1 Pentium-II, Pentium-III, Slot-2 Pentium-II/III Xeon 等. Intel Pentium-II 继承了 Pentium PRO 的运算核心, 但当时的 IC 工艺还无法将庞大的 cache RAM 放进 die 里头, 这个技术即使是现在也放得不多. 在此之前 586 Pentium 的 L2 cache 是放在主板上的 64Kx64-bit SRAM. 以理论上来讲 on-die cache 自然好过 on-board cache, 因为靠得近嘛. 既然当时的 IC 工艺办不到这点, 那该怎么提高效能呢? Intel 的克服方法就是由技术领先的自己先把这两个东西集成好做成模块, 然后再卖这个模块. 如此一来, 威名赫赫的 Slot-1 便摇摇晃晃的出场了, 好大一颗 CPU 啊! 类似的技术也运用在服务器级的 Slot-2 Xeon 上.

Intel SECC2 Slot-1 Pentium-III CPU

Intel Slot-2 Pentium-III Xeon CPU

Intel MMC : CPU and Northbridge on Single Module

Intel MMC (Mobile Module Connector) 是 Intel 在 TCP (Tape Carrier Package) 之后针对笔记本应用所发展出来的规格, 之后还历经了 MMC1 与 MMC2 的改版. MMC 在 Pentium MMX 后期便被提出, 用以取代原本使用的 TCP 技术, 并一直使用到 Tualatin 技术完全成熟才除役. MMC 的产品概念是将 CPU, L2 Cache 与北桥芯片 (Northbridge) 集成为模块, 以简化笔记本的设计难度. MMC 模块由于已经将 Northbridge 包进去了, 与主板间的连结变成只有 Memory Bus 与 PCI Bus 等信号, 后期再加入 AGP Bus 的定义脚.

Intel MMC2 Moblie Pentium-III CPU

发现了吗? 其实在今年 IDF 中出现的东西, 和 MMC 在产品概念上是相同的, 只是新一代可运用的技术有所进步. 也就是说, SECC 的产品概念是 CPU and L2 Cache on a single chip, 现在的 IC 工艺可以做到 on-die L2 cache. MCC 的产品概念是 CPU, L2 Cache and Northbridge on a single chip, 虽然现在做不到 on-die Northbridge, 但可以透过 multi-die on a chip 的 IC packing 技术达到 single chip.

咳咳, 好像本来是要说 multi-die on a single chip 的 IC packing 技术的, 怎么一不小心跑题跑得老远了. 咳咳咳, 简单交待一下, 回到前面 IC Packing 技术的部份. 传统的封包技术中的 wire bonding (打线, 一般是打金线) 难以克服现在高密度的 IC pin-out 与 chip size, 因此 Intel 提出 FC (Flip Chip) 的概念, 也就是现在的 FCPGA, FCBGA, Micro-FCBGA 等的封装方式, 将 wire bonding 变成将 die 直接打在 chip 里的 PCB 上, 不必再辛辛苦苦的拉金线了. 如此一来要将两个 die 封包在一个 chip 里头的需求便可透过高精度的 Flip Chip PCB 来达成, 连猴子也... 哦不, 是连 VIA 也办得到. (VIA 的 IC 制造是外包, 也就是他的外包厂办得到.) 若要以传统 wire bonding 来做的话必须以金线连接两个 die, 何况又是 CPU 和 Northbridge 之间的高频 host bus, 几乎是 Mission Impossible!

Maybe continue...![]()

![]()

![]()

- 相关回复 上下关系8

【原创】在 Multi-die IC Packing 技术面世之前

😄问 马鹿 字604 2005-09-01 20:42:53

😄【回答】DRAM None-Marking IC 的交易模式与 Remark 30 四月一日 字4156 2005-09-01 22:27:26

又遇到一个问题: refurnished指什么? 马鹿 字0 2005-09-04 09:34:44

😄总结:还是要买名牌。 马鹿 字72 2005-09-02 08:10:59

😥Not at all, 看性价比吧. 10 四月一日 字0 2005-09-03 08:18:31

😄买骗[片]子的时候又不知道真骗子还是假骗子 1 马鹿 字13 2005-09-03 08:20:29

😄Try and error. Learning by doing. 8 四月一日 字18 2005-09-03 08:21:43